�Ĕ����D�Q�Ы@ȡ�������

��ǰλ�ã���� >> �x���x�����g����

�Ĕ����D�Q�Ы@ȡ�������

����܇��ӿ����·���棬�������ԄӸ���ϵ�y����ӷ����Գ����ϣ�ģ�M�c�����D�Q���|�ش_��������һ��֮�����κε��t�����߲��ʴ_�����p���ھo����r�±��o܇�v�˿͵��������mȻ�@��һ���O�����ӣ����s�f���˔����D�Q�|����Λ_���Á�����ģ�M��Ӿ�·�Ĕ���̎��������K���ܣ��ʴ��@��һ�����ݺ�ҕ���n�}��

�D�Q�|����K�������õ�ģ �� ���D�Q����ADC������ �� ģ�D�Q����DAC�����|�أ�֧ԮԪ�����Լ�����̖�·�������õļ��g�OӋ��֧�估�Q����

�ɱ�Ҳ�����̘I�lչ�����ԃ�����|�ص�һ�����}���aƷ�A�㼴���f�Ҍ����ṩ��ѳɱ� �� ���ܱȵ�Ԫ�������⣬ͨ�^���ּ������}���l���ձ��`��Լ��������벻���ļ��g���y������Ӱ푵��OӋ��Ч�ʺ��c����Ԫ�����P���|�أ����ɱ�����

����Ŀ����Ҫ������ADC��DAC���F������֮�y�Q��ADC�������ҵ������ձ�����`���Դ�^������Microchip��National Semiconductor�ɼҹ�˾�Ęӱ�Ԫ���酢�ա����ҕ�Ԕ��ӑՓ�����ӱ������·��

����Ҳ�����Ҋ��ʹ����I���������[�������x�������κ����@�����܆��}��

�`��֮Դģ�M�c�����D�Q�`��ɷ֞��cֱ����DC����������AC�����P���`�DC�`���ּ��֞���������`��־����`��e�־����`�ƫ���c�����`�AC�`��һ���c���뼰���C��ʧ�棨THD�����}���P��

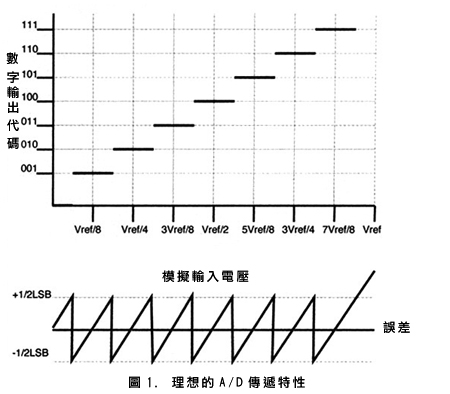

������������`��ÈD1��ʾ�ĺ���3bit�D�Q�����f����ݔ��늉�����������8���xɢ�ƽ�턝�֣��քe�ɴ��a000��111ȥ����������ÿһ���a��ԽVref/8 ��늉���������n bit�D�Q�����v�@����Vref/2nӋ����������a��Сһ�㱻���x��һ�������Чλ��LSB�������ٶ�Vref = 8V��Ԓ��ÿһ���a֮�g��늉�׃���ʹ���1V���Q��֮���a��ָ�����a�Č��H늉��c����ԓ�a��늉�����֮�g�����`�һ����v��0.5LSBƫ�Ƽ��뵽ݔ��˱㌧���������^���c����+/-0.5LSB�������`������������м�����+/-0.5V�`�

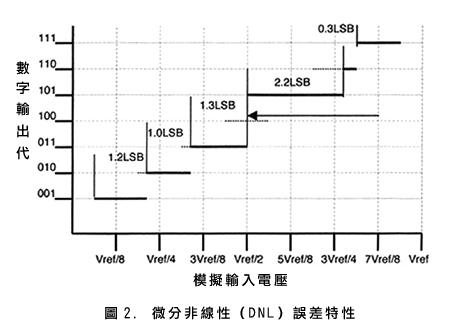

��춈D1��ʾ��һ��������D�Q������a���a�^���c���1LSB��Ȼ�����ڌ��HADC������r�����@�ӣ����F���ַǾ��ԣ�DNL���`�����D2��ʾ�����a010��011֮�g�^����һ��0��DNL����鄂��1 LSB�����ǣ�000��001�^�ɾ���һ��+0.2 LSB��DNL��������1.2 LSB�Ĵ��a���ȡ�����DNL�`�ָ����+/- 1 LSB��Ԓ��ԓ�D�Q���Ϳ�����©ʧ�a�����a100�������F��ݔ���ˣ�����D�Q���o���a101��2.2��DNLֵ�Ñ�Ҫע�⣬�ڔ���������]������f��DNL���ֵ�Ԓ����ҕԓ�D�Q����]��©�a����ʾ���Ѓ��+/- 1 LSB��DNL���֣�Ʃ��Microchip MCP320X 12 bit�D�Q��ϵ���ڔ�����ӆ����+/- 1 LSB DNL��

�����D�Q��������һ���]�h����ϵ�y���棬���ӵ�DNLӰ푕����ϵ�y����Ғ�������O���c�܇��u�[��������δ���oֹ춷�����r����Ҳ�ݱؽ�������ȣ�SNR����

���W�e�ֵ�DNL

Ȼ�������dz���һ��Ҫ�x����+/- 1 LSB DNL��ADC��Ʃ��һ����+/- 4 LSB DNL��16 bit�D�Q������14 bit�]��©�a���m�������13 bit�ֱ��ʵ��OӋ������]��©�a��16bit�D�Q��������ˡ�

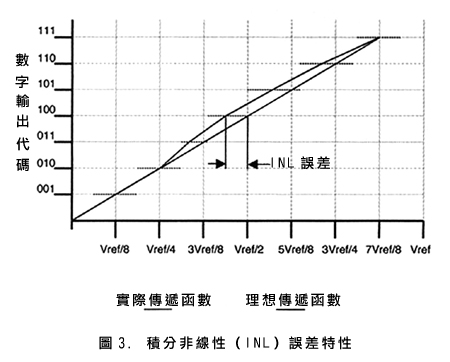

�e�ַǾ��ԣ�INL����DNL�`��Ĕ��W�e�֣������fһ����������INL��ADC���C�����õ�DNL��INL�������D�Q���c���뾀�Ԃ��f������ƫ���D3��ʾ���������ձ��ЃɷN��ͬ����ȥ�y��INL������OӋ���ġ����c����������m�䡱������Ҫ�Ɣࡣ

���ԡ�����m�䡱�����v������m�侀�Ԃ��f������ԓ����INLƽ����f��������ؓƫ������������@������˱��ɡ�ĩ�ˡ��������õĸ���INL���֡�Ȼ�����ڌ��H���О�Ҫ���F�@Щ���֣�ʹ���߱�횞����漰ƫ���`���{��ÿһ�D�Q������춴�����OӋ�����v�@�Dz��Ќ��H������ϣ���ġ�

��춶��c���������Ԃ��f���������^�cβ�a�^�ɵ��B���ρ����x��INL����ָ���c�@����ƫ����m�o�һ�������صĽY��������ʹ���߸������ã���ֻҪ�ɶ��c�����{������o�������INL�����r����˾��National Semiconductor���á����c�����������INL�cDNL���߶�����У�ʻ����������ԣ����x��һ��������ָ���`���A���ADC�r�������Ǻ���Ҫ�ą���������

�����cƫ���`��Ҳ�l����ADC�D�Q�����棬���s��������������У������ƫ��늉��`����ָ������ݔ�����a���c���a�^���c��ƫ�ͨ���ڵ�һ�����a�^���c�Ϝy����ֵ�������������D�Q���ÆΘO�Է�ʽ��Ԓ���mȻ�@�`�����У�������������ӑB������һЩ�pʧ�������`��x���c����ģ�M-���ւ��f������ƫ��_����ĩ���a�^���c������ƫ���`��ֵ�pȥ�������Ӌ�����ֵ�`������`��Ҳ�c�����õĻ���늉����P���ʴˣ�ע�┵�����Ƿ���ÃȲ��ֻ��ⲿ����늉����Q�������`�������Ҫ��

�Еr������һ���ց��f���������ȫδ�{���`���^���`��@�������`���Դ��Ҏ�����o���OӋ���_��Ԫ���Ƿ����ij�ض��`���A��������Mһ��У�ʵ�ֱ�ӷ������ݔ��������o�Ա����`���Ҏ���Ա��OӋ���xȡһ�����ϼȶ��`���A���Ԫ����

AC��̖

�������`���DZ��_�D�Q����DC���̶ܳȣ�����OӋ��Ҫ�_��һ��ʹ��AC��̖��Ԫ����Ԓ����횿��]�Î������늚����ԡ���ҪҎ��������ȣ�SNR���������cʧ��ȣ�SINAD�������C��ʧ�棨THD�����o�����ĄӑB������SFDR������Чλ����ENOB������ĩ��һ��������������ӑB���ܵ�Ҏ��

SNR��ݔ����̖�����ݔ�����ı�ֵ�����в��������C����DC�ڃȡ��@���������������N�ɷ֡������D�Q�������a�����������������������Pϵ�����Q���ķֱ��ʣ��D�Q�����������Ҫ���cݔ����^�����ܵ����Ƴ̶����P������@���ʴ_��ʹ�ߵĉ��[���½�����ֵ������SNR�����x���l�ʡ���Փ�����SNR���

SNR max��dB��= 6.02n + 1.76

ʽ��n = �D�Q���ֱ��ʣ�bit��

THD�˱�ʾ�D�Q���ľ��Զȣ�������_�䌦��̖���C�����������û�Ӱ푡������C���ͷ�����root-sum-square������Чֵ���������������ݔ�����Чֵ��RMS����

�ڔ��������Ҍ������õĔ�ֵ��SINAD���������_ADC���M�����C����ʧ��ij̶ȡ��������D�Q���С�SINAD�cSNR����ͬ�ġ���SINAD�����D������Чλ����ENOB�������D�Q���|���и���һ�c�����x�ĸ�����^�����S�����������䔵�����б���ENOB�����ߵ��Pϵ���

ENOB = ��SINAD - 1.76��/6.02

ENOB�˴��������D�Q�����е�λ���ֱ���ȥ�o�c��ͬ��SINAD����Ҫ������ָ��ȡ���l�ʼ��yԇ�l�������l�ʽӽ��ο�˹�أ�Nyguist�����ʕrENOB���½�������SNR�ķ����nj��Pע����̖�����^ȡ�ӣ�ÿ��ȡ���l�ʼӴ�һ�����ױ㽵��3dB��

SFDR�����x������ݔ����̖����Чֵ�c������ݔ���l�ʣ��������ݔ��ˣ��IJ�ֵ�����OӋ�����v�@�Ǻ���Ҫ�ģ����f�����D�Q�����Էֱ������̖�ƽ��

�·�OӋ���}

�����˽�ADC��������ζ��x�`��F�ڸ���Ҫ�������ײ��ӵ��·�OӋ��·��ؓp���D�Q�������ܡ����̖Դ�cADC֮�gͨ����Ҫ�M��ijЩ��̖����̎�������в����κ������������������x�õĔ�ֵ��ȡ���H��ֵ��

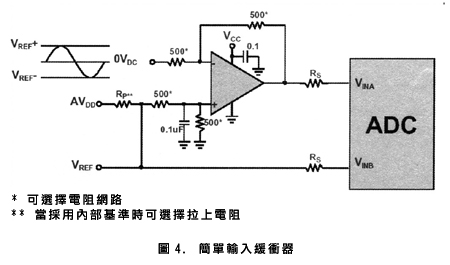

�D4��ʾ�麆�εľ��_������Ҫ�����������ţ���Ԫ��֮�g������H�ߡ��Ɍ��¸��l��ϵ���̖·�����������ݔ���t�c�B�����\�����˵����֮�g����ݿ������ʎ���@�����F��һ��DCƫ�ơ�

�\�ŵ��x��Ҳ����Ҫ��Ӱ�ϵ�y���ܵķŴ���Ҏ����ƫ���`��늉���ݔ����ϵ�y����̖����̎�����_��߀�������y�����Ć��}��

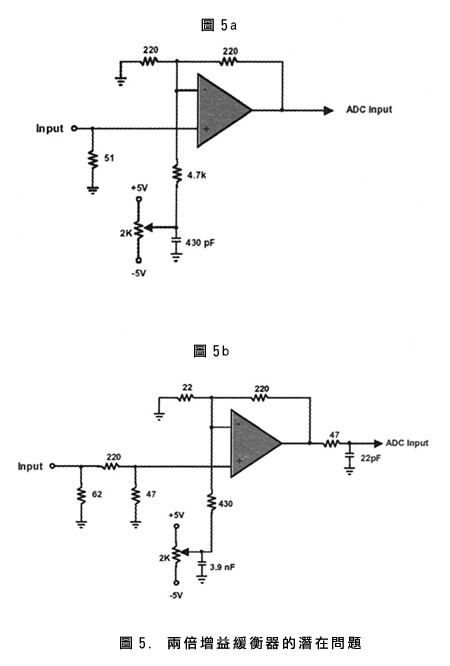

�D5a��ʾ��һ������2������ľ��_�����@���Ѓɂ����چ��}�����ȣ������ȡ��ADC��ݔ�����һ���_�Pʽ�����ؓ�ɣ��@��·���ԏ�ݔ�����_ݔ���������ʴ��������˷Ŵ���ݔ����⏻���ʎ���п��ܵġ����ķ��A��ʩ����RC�W�j����ݔ������ϣ���D5b��ʾ��

��Σ��Ŵ��������һ���������ϣ��������������ʎ����ݔ����̖˥�p�������Ŵ����������ͻ�@�@���}��

���m�����Դ�����Ҳ�Ɍ��²��ӵĔ����D�QЧ�ܣ���ADCݔ����׃��B�r��ݔ����������ȡ�ܴ�ӑB�����������ҪͻȻ�g�����ؓ�ɣ����e�Ѓɗl·������������ȣ���ݔ���R�����κ����ͨ�^Ԫ���r�ף�оƬ�أ������ҿ���ɹ���ģʽ����鮔�����D�Q�r�@��늉���ݔ����Ч�pȥ���p��ADC�c̎����֮�g�ľ��x�����ô���裬���������@��Ӱ푡�

��Σ����ݔ����Դ�������N�@Щ���������������_�������������ģ�M�c�����Դ���_�]���m��������@��ʹ���ȥģ�M�·��

���õ�����Ϸ���

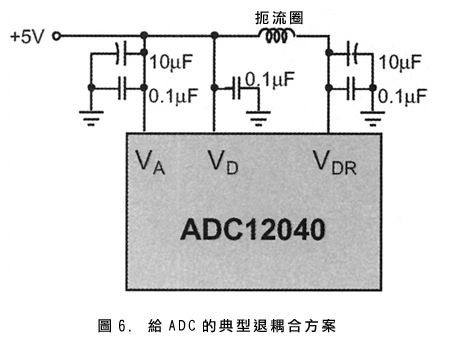

�D6��ʾ��oNational ADC12040��һ����������Ϸ��������x���Ѓ����Դ���Ʊȣ�PSRR����ADC�;��_����ɜp���@Ӱ푣��������PSRR���S�l�����Ӷ��½�����

���õ�ƽ��Ҳ�nj��p��������̎�����^����ע��Ҫ�_����ƽ���ϵ��g϶�c��̖·��ƽ�С�

���Õr犁����D�Q��Ҳ�����һЩ�p�ʴ���Ć��}���ו���ϵ���̖·�����������ܣ��ʴˣ�������·����Ҫ�h�xģ�M��̖�������r����^����ӣ����@�F�����c�ܵ�ռ����׃����������и��@����Ӱ푡��@Щӕ���춲��ֲ�r犾����@���_�˽ӣ��Լ��r��·�OӋ�������¡������������ǰѕr犾�������ݔ�����������ҽo�����_�˽ӡ����·���L��������ɵ����t�dz�Խ6���r������r�g��Ԓ���ͱ�Ҫ�@������FR4��������tһ��ÿ����6ps���Q��֮����2ns�����r�g����̖���v���L�ȳ��^55���ĕr犾��ͱ��ҕ�����ݔ�������o�����_�˽ӡ�

�����·

�����춿��]���·�ǻ���Դ������Դ���|�،�ϵ�y���ܾ��ش�����x��ԭ����ģ�M��̖������������^�����������@����������ʼ�ʴ_�ԡ��ض�ϵ����ݔ������Ʃ�磬�OӋ����һ�������-40����+85��ضȷ�������12 bit�ʴ_�ȵ�ϵ�y�����ʾ���Ҫ���4ppm��

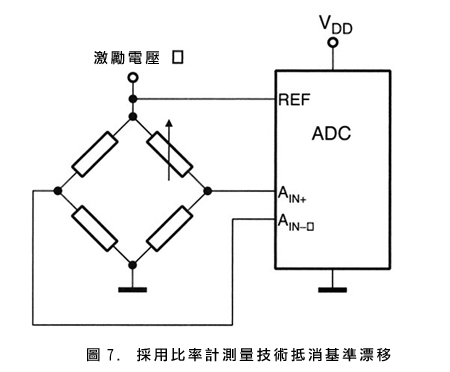

��һ�N���g�ɜp�͌�����Ư��Ԫ���������@�Dz�����D7��ʾ�ı���Ӌ�y�������ʰ��������BͬADC���룬��Ч�ص�������늉��ϵ��κ�Ư�ƣ�����һͬӰ�ADC�cģ�Mݔ�롣

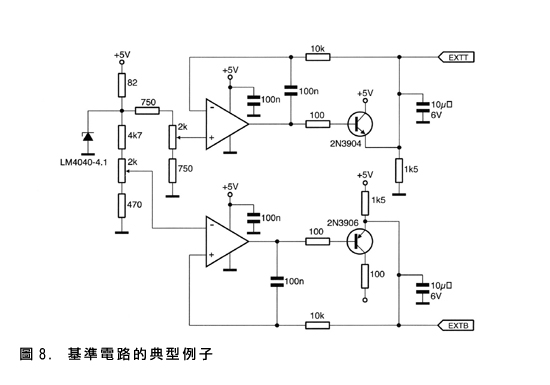

�D8��һ�����͵Ļ����·�����Á��ӿ����National ADC1175֮ĵ���ADC������ݔ���������_�����ṩADCݔ������ĵ��迹�ӡ��x�õ�������蔵ֵ��Ҫ���ͣ��ű��C���ʶ��O������ضȷ������е�Ư�ơ�

��������

�@����Ҋ����ʹ��ADC�OӋ֮�r���S�����ڵ��`��Դ�^��ÿһ�����������w���ܼ����óɱ�����ۿۡ�Ȼ����ֻҪ������Щ�ձ靓�ڵ��韩�ط����Ϳ��Ժ�����֮�R�e�����_����

�@����Ҫ���P�^����锵���D�Q���܌���K���ü��aƷ�ě_��������̘I�ϵijɹ�����ֱ��Ӱ푡�

�������P��Ϣ

- ��Ώ�PAR�_��DLI��ÿ�չ�e�֣�

- �y�������е��չ�e��(DLI)�̘I���ґ���

- ���QU26-001�ܽ���ӛ䛃x������ñU26-RDOB-1�IJ������E

- �u��������̼����ӛ�����5����Ҫ���]����

- ������׃���Ƿ�������Z�L

- ����ӛ䛃xMX2200ϵ�е�һЩ���}�ͽ��

- �{��ˮλӋMX2001��ͬˮλ�����c���xȡ�ͅ���ˮλֵ�O���f��Ԕ��

- Onset���|�������wϵ

- ����ɺ����һ���¸ҵ�������ɺ����

- ����ˮ�ւ�����S-SMD-M005��S-SMC-M005����ԭ�탞�c�ͅ^�e

����c������

- 1500��ˮ�ض�ӛ䛃xMX2204 HOBO TidbiT MX Tempe 5000

- HOBO�o���{��ˮ�ض�ӛ䛃xMX2203 TidbiT MX

- MX2201�¿�{��ˮ�ض�ӛ䛃xPendant MX Temp

- ���������ܟ���Fotric816/Fotric826

- ���̎�ͨ�ß���xFotric 222s/Fotric 222s-1/Fotric 222s-2

- HOBO MX100�{���ض�ӛ䛃x��ˮ�ȼ�IP67

- �ɳ�ʽ����ӋTES-1352S��ӛ䛿ɲ�SD��

- ����ӛ����նȹ�����ӋTES-1339P

- ��yһ�wʽ�؝�ȴ�≺��ӋTES-1160/TES-1161

- �߾���ˮλӋMX2001-04-s���o��������ݔ